消費電力「数十万分の一」、ハード実装の次世代ニューラルネット

スタンフォード大学の研究チームは、論理ゲートを利用してニューラル・ネットワークを構築することで、エネルギー消費量を大幅に削減する方法を発表した。最終的には「ハードウェア基盤モデル」と呼ぶものを作りたいと考えだ。 by Grace Huckins2024.12.23

- この記事の3つのポイント

-

- 低消費電力なコンピューターチップ上の論理ゲートネットワークが開発された

- 訓練には従来の数百倍の時間を要するが一度訓練すれば大幅なコスト削減が可能

- 開発者は効率性を追求し、将来的にはパーソナル機器に組み込むことも目指している

コンピューターチップのハードウェアに直接プログラムされたネットワークは、現代のほとんどの人工知能(AI)システムの基盤となっている従来のニューラル・ネットワークよりも高速に画像を識別でき、消費電力もはるかに少なくて済む。このような研究結果が、バンクーバーで12月10~15日に開催された機械学習分野のトップカンファレンス「神経情報処理システム(NeurIPS:Neural Information Processing Systems)2024」で発表された。

GPT-4からステーブル・ディフュージョン(Stable Diffusion)に至るまで、ニューラル・ネットワークは、人間の脳内のニューロンを高度に単純化したシミュレーションであるパーセプトロンを多数つなぎ合わせて構築されている。膨大な数のパーセプトロンで構成されるニューラル・ネットワークは高性能だが、膨大な量のエネルギーを消費する。マイクロソフトはAI開発に必要な電力を得るために、スリーマイル島原子力発電所を再稼働させる契約を結んだほどだ。

問題のひとつとして、現在のパーセプトロンが単にソフトウェア抽象化したものにすぎないということがある。GPU(画像処理装置)上で多層パーセプトロン・ネットワークを実行するには、そのネットワークをハードウェア言語に翻訳する必要があり、それには時間とエネルギーが必要となる。ハードウェア・コンポーネントから直接ネットワークを構築すれば、こうしたコストの多くを削減ができる。将来的には、スマホやその他の機器で使用されるチップに直接組み込むことも可能になり、サーバーとの間でデータを送受信する必要性が激減するかもしれない。

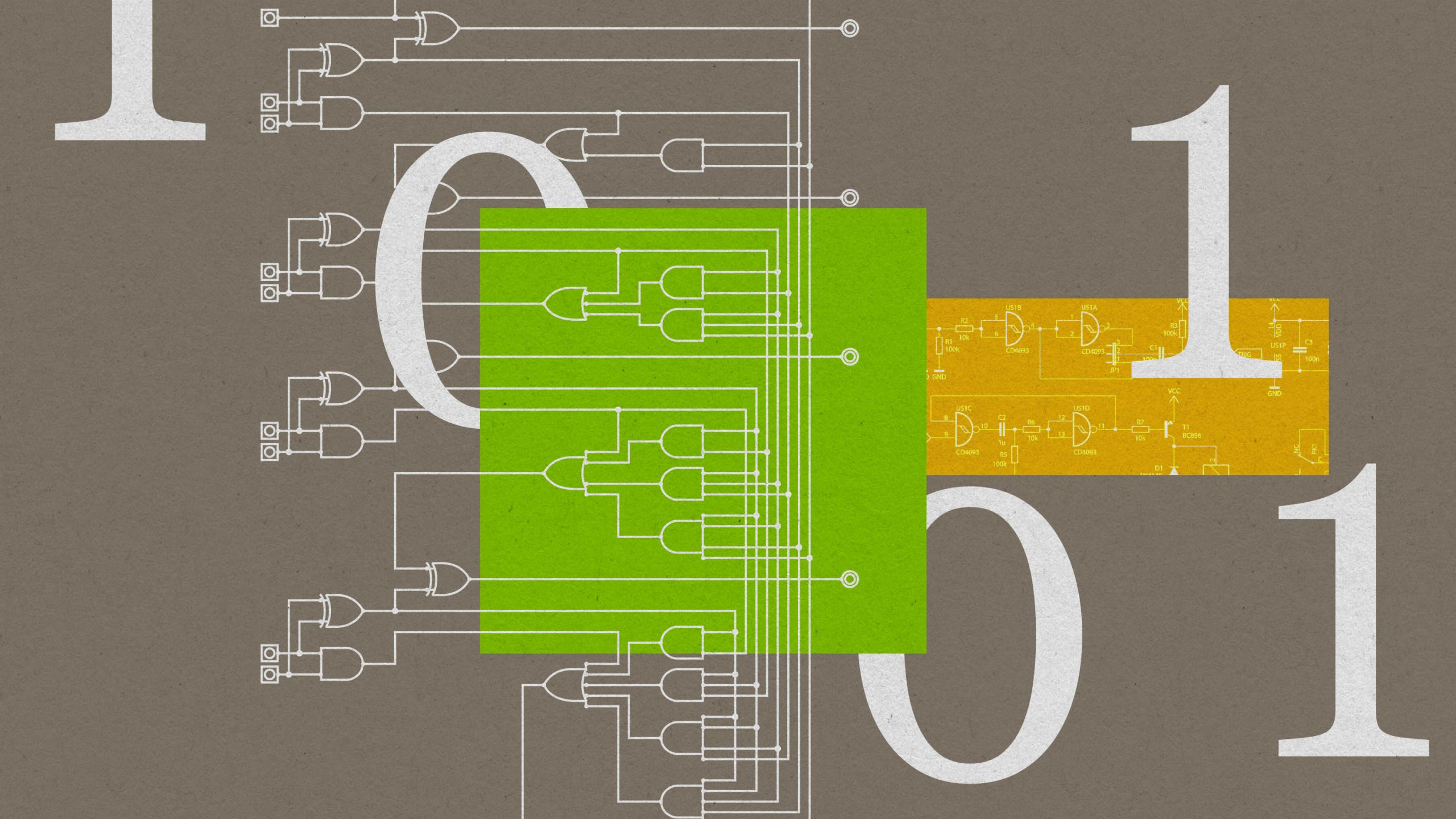

スタンフォード大学の博士研究員としてこの研究をしたフェリックス・ピーターセンには、それを実現するための戦略がある。ピーターセン博士は、コンピューターチップの基本的な構成要素のひとつである論理ゲートで構成されたネットワークを設計した。各論理ゲートは数個のトランジスターで構成されており、入力として2ビット(1または0)を受け取り、トランジスターの特定のパターンによって決められる規則に従って1ビットを出力する。パーセプトロンと同じように、論理ゲートを連結してネットワークを作ることができる。そして、論理ゲート・ネットワークの運用は、簡単、高速、安価だ。今回のNeurIPSの講演でピーターセン博士は、論理ゲート・ネットワークのエネルギー消費量はパーセプトロン・ネットワークの数十万分の一だと述べた。

論理ゲート・ネットワークは、画像ラ …

- 人気の記事ランキング

-

- A Google Gemini model now has a “dial” to adjust how much it reasons 推論モデルは「考えすぎ」、グーグルがGeminiに調整機能

- What is vibe coding, exactly? バイブコーディングとは何か? AIに「委ねる」プログラミング新手法

- Meet the researchers testing the “Armageddon” approach to asteroid defense 惑星防衛の最終戦略 科学者たちが探る 「核爆発」研究の舞台裏

- Anthropic can now track the bizarre inner workings of a large language model 大規模言語モデルは内部で 何をやっているのか? 覗いて分かった奇妙な回路